ENGINEERINGNET.BE - Dans cet article, Naoto Horiguchi, directeur de la technologie des transistors CMOS à l'imec, met en lumière le développement du transistor nanosheet depuis ses origines jusqu'à l'arrivée des nouvelles générations, à savoir les transistors forksheet et CFET. Cette gamme de nanofeuilles permettra une miniaturisation supplémentaire des puces de calcul pour répondre à la demande toujours croissante de puissance de calcul.

Le nombre de transistors sur une puce double environ tous les deux ans, accroissant à chaque fois la puissance de calcul disponible sur une surface plus restreinte. Rendre les puces de plus en plus puissantes est requis pour apporter une réponse au trafic croissant des données et permettre les innovations. À un moment donné, cependant, les limites physiques sont atteintes et de nouveaux transistors doivent être développés pour poursuivre cette réduction d'échelle.

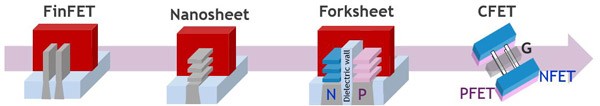

Aujourd'hui, le transistor FinFET est intégré dans les puces les plus avancées pour les applications de calcul (la générations des technologies à 5 et 7 nm). Le FinFET tire son nom du fait que la région source/drain est formée d’ailettes (‘fins’ en anglais). L'industrie des puces sollicite rarement l'adoption d'un nouveau type de transistor pour la production en masse de puces. Cela rend en effet le process en production beaucoup plus complexe et implique des investissements supplémentaires.

Mais récemment, certains grands fabricants de puces tels que Samsung, Intel, TSMC et IBM annonçaient qu'une telle transition était imminente. À partir de 2022 - 2023, ces entreprises ‘transiteront’ progressivement du transistor FinFET usuel aux transistors à nanofeuilles. Ces derniers seront le cœur battant des puces de calcul de la génération technologique à 3 ou à 2 nm.

Pourquoi transiter du FinFET à la nanofeuille ?

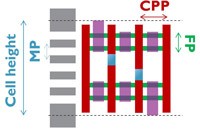

Une manière d'obtenir de plus en plus de transistors sur la même surface de puce consiste à réduire la taille des cellules standard. Une telle cellule est une petite unité fonctionnelle d'une puce qui peut exécuter une fonction logique limitée, AND ou OR par exemple. Une cellule standard se compose de quelques transistors et de quelques couches d'interconnexion métalliques pour les connecter entre-eux. La réduction de taille d'une cellule standard peut se faire en réduisant la ‘hauteur’ de la cellule.

Pour un FinFET, cela se fait en réduisant systématiquement le nombre d'ailettes par transistor. Dans la conception originale du FinFET, trois ailettes étaient utilisées pour avoir une densité de courant suffisante. Mais pour réduire davantage la cellule standard, ce nombre a été réduit à deux. Pour maintenir une densité de courant suffisante, les deux ailettes ont été légèrement surhaussées. Cette tendance pourrait se poursuivre jusqu'à ce qu'il ne reste qu'une seule ailette. Cependant, augmenter encore la densité de courant des architectures de transistors FinFET est une gageure.

Et c'est là que l'architecture à nanofeuilles vient à la rescousse. Dans ce transistor, le canal de conduction a la forme d'une très petite ‘feuille’ appelée nanosheet. Il est actuellement possible d'empiler plusieurs nanofeuilles verticalement les unes sur les autres et rendre chacune des nanofeuilles un peu plus large. De cette manière, plus de courant passe dans le transistor qu'avec un FinFET, sans avoir à augmenter son empreinte.

Un autre avantage important de la nanofeuille est la structure dite ‘gate-all-around’ (GAA) : la grille (gate) du transistor entoure entièrement les canaux de conduction, alors qu'avec le FinFET ce n'était le cas que sur trois côtés. Cela permet à la grille d'exercer beaucoup plus de contrôle sur le canal de conduction ; cela se traduit par moins de courants de fuite lorsque le transistor est inopérant. La nanofeuille offre donc également une solution pour les ‘effets de canal court’ indésirables qui se produisent dans les très petits transistors.

Blocs de construction critiques

Tout comme lors de la transition du transistor MOSFET classique au FinFET, un certain nombre de nouvelles étapes de process ont dû être développées pour la transition du FinFET au transistor à nanofeuilles GAA. Heureusement, ce nombre de jalons était limité, car la nanofeuille découle naturellement du FinFET du point de vue fabrication. Bien des modules de process qui ont été en son temps développés et optimisés pour le FinFET pouvaient donc être réutilisés. Et cela a certainement facilité le changement imminent pour l'industrie.

Cependant, il existe un certain nombre d'étapes critiques du process pour lesquelles les deux architectures diffèrent et qui nécessitent des innovations spécifiques. Dans une première étape du process de fabrication, différentes couches de Si et de SiGe sont superposées en alternance. Le SiGe sera éliminé par morsure dans une phase ultérieure, après quoi persisteront plusieurs canaux de conduction en Si (empilés verticalement).

Cet empilement multicouches est transformé en une structure haute et étroite au moyen de techniques de gravure, rendant difficile le maintien de la forme de la nanofeuille. Imec a présenté lors d'une conférence de renom (IEDM) en 2017 une solution pour cela qui a également conduit à de meilleures performances des transistors : un courant plus fort et une commutation plus rapide. L'imec a également été le premier à signaler l'intégration d'un transistor à nanofeuilles fonctionnant correctement dans un circuit réel (un oscillateur en anneau).

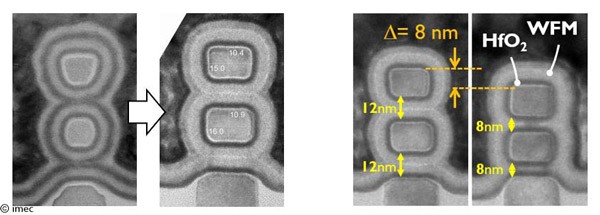

Les autres étapes critiques du process sont : la création de l'inner spacer (module destiné à isoler la grille de la source et du drain) ; l'étape channel release (au cours de laquelle les nanofeuilles sont séparées les unes des autres par morsure sélective des couches de SiGe) et l'intégration de la structure de grille (dans laquelle le métal de grille doit être appliqué entre et autour des nanofeuilles).

L'architecture forksheet prend le relais

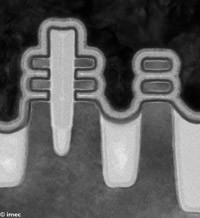

La meilleure façon d'améliorer le fonctionnement des transistors est d'augmenter encore la largeur effective des canaux sans surdimensionner la cellule standard. Mais c'est très difficile dans les architectures nanofeuilles conventionnelles. Le trouble-fête est le grand espace requis entre les transistors de type p et n (les deux types sont requis dans une puce de calcul CMOS standard). Et c'est là que le transistor forksheet vient à la rescousse. Cette architecture, inventée par l'imec, permet de rapprocher les transistors de type n et p en plaçant un diélectrique entre les deux types de transistors.

L'espace libéré peut ainsi être utilisé pour augmenter encore la largeur effective du canal, augmentant ainsi le courant. Ou, le plus petit espace entre n et p peut être utilisé pour réduire à nouveau la hauteur de la cellule standard. Le designer a donc la liberté de jouer avec ces paramètres. Les simulations prédisent également que le forksheet pourrait commuter plus rapidement qu'un transistor à nanofeuille ordinaire. Du point de vue de la fabrication, l'architecture forksheet découle naturellement de celle à nanofeuille conventionnelle.

Bien qu'il y ait également ici un certain nombre de nouvelles étapes de process ; la création du diélectrique par exemple. Lors d'une conférence de premier plan (VLSI 2021), était explicitée l'intégration réussie pour la première fois des transistors forksheet, ainsi qu'une caractérisation électrique. La distance entre les transistors de type n et p pouvait dans ce cas être réduite à seulement 17 nm. Une préoccupation subsistait cependant. Comme expliqué précédemment, la structure GAA est un atout important de l'architecture nanofeuille.

Elle permet en effet un meilleur contrôle électrostatique du canal de conduction. Pour le forksheet, la structure de la grille a la forme d'une fourche - d'où son nom - et n'entoure le canal que par trois côtés. Cependant, l'imec a pu démontrer que le contrôle du canal d'un forksheet (avec une longueur de grille de 20 nm) est comparable à celui des transistors à nanofeuilles empilés verticalement.

À plus long terme, le CFET pourrait compléter la famille des nanofeuilles

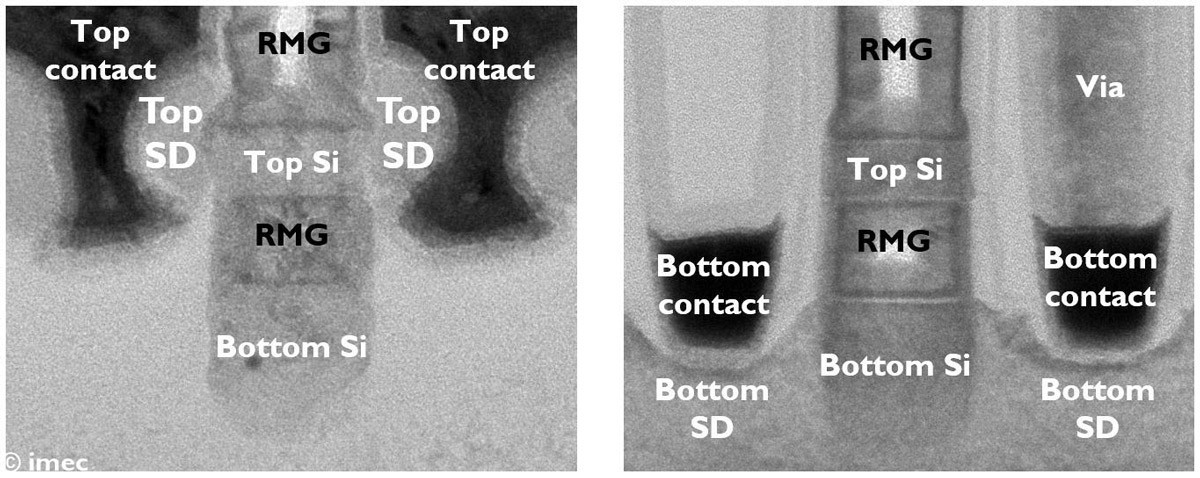

Avec le transistor à effet de champ complémentaire ou CFET, nous pourrons encore augmenter plus la largeur effective du canal. Dans cette architecture, les transistors de type n et p sont empilés les uns sur les autres. De cette manière, la distance entre les transistors de type n et p se déplace maintenant verticalement, et nous n'avons plus à en tenir compte lors de la détermination de la hauteur de cellule.

De l'espace est ainsi libérée pour augmenter encore plus la largeur du canal. Le gain de surface peut à nouveau être utilisé ici pour réduire encore plus la taille de la cellule standard. Dans le CFET, les canaux peuvent être réalisés sous la forme d'une ailette (n-fin sur p-fin) ou sous la forme d'une nanofeuille (n-sheet sur p-sheet). Dans cette dernière configuration, le CFET complète la famille des nanofeuilles en tant qu'architecture de transistor CMOS ultime. Cependant, l'architecture CFET est relativement complexe à créer.

Pour permettre une intégration verticale des deux types de transistors, on peut suivre deux schémas d'intégration possibles (monolithique et séquentiel) chacun ayant ses avantages et ses inconvénients. L'imec se concentre sur le développement des modules spécifiques et les étapes d'intégration et cartographie les avantages et les inconvénients de chaque flux de process.

Conclusion

Dans cet article, nous avons expliqué comment l'architecture nanofeuille permet une réduction d'échelle supplémentaire des puces de calcul. Chaque nouvelle génération, rendue possible par la nanofeuille, le forksheet et le CFET, fournit des transistors de meilleure performance et/ou une réduction supplémentaire de hauteur de la cellule standard.

Du point de vue de la fabrication, la nanofeuille découle naturellement du FinFET. Pourtant, chaque architecture de nanofeuille pose des défis d'intégration spécifiques. L'imec reste déterminé à développer des solutions à ce sujet, à peser le pour et le contre et à rendre compte des résultats à ses partenaires de l'industrie des puces.

Cadre: Au sujet de l'auteur

Naoto Horiguchi est le directeur du programme ‘logic CMOS scaling program’ à l'imec. Il commençait sa carrière en 1992 dans la R&D des semi-conducteurs chez Fujitsu Laboratories. De 1992 à 1999, il s'est concentré sur le développement de transistors chez Fujitsu Laboratories et à l'Université de Californie à Santa Barbara. De 2000 à 2006, il a dirigé le développement de la technologie CMOS 90-45 nm chez Fujitsu en tant qu'ingénieur d'intégration.

Il travaille à l'imec depuis 2006. Il s'y concentre sur la recherche et le développement de transistors CMOS avancés en collaboration avec l'écosystème mondial de partenaires industriels, d'universités et d'instituts de recherche d'imec. Il se concentre actuellement sur la réduction d'échelle des transistors CMOS pour les nœuds technologiques de 1 nm et plus petits.